# INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY

# Single Electron Transistor based Hardware designing of Linear Block Coding Technique for Error Correction in Digital Communication System

Jayanata Gope \*

\* Electronics and Telecommonication Engg. Dept, Jadavpur University, India

jayantagope@rediffmail.com

#### Abstract

An increasing success in e-beam lithography technique revolutionized low power consuming, high integration density next generation nano device built consumer electronics. This has inspired Researchers to design several nanoscale devices such as Single Electron Transistor (SET) made Single Electron Devices (SED) that can be included in near future in every sphere of life. One such unique approach of the Researchers is to introduce SED in Digital Communication System. The major challenge faced by the Researchers is the unintentional error that often occurs in the receiver side of any Digital Communication System. It is essential to detect the error and correct it simultaneously during transmission. Several solutions have been reported so far in numerous research journals regarding this. Among other popular error correction techniques, the method opted here is Linear Block Coding Technique for error correction because of its unique feature of time consuming and efficient error detection process. Here the approach is to design a Single Electron Device based model of this error correction technique so that to incorporate it in near future for low power consuming Digital Communication System.

**Keywords**: Single Electron Transistor (SET), Single Electron Devices (SED), e-beam lithography, Linear Block Coding Technique, error correction technique, Digital Communication System.

#### Introduction

Low power consuming, high speed & high integration density SETs play a major role in modern nano scale electronics. SET based SEDs are one of the excellent examples of nano electronics technology. One single electron is suitable to accumulate one bit of information in the SET, this is why the Researchers emphasize most in manipulating electrons at a larger scale. In other words controlling the transport of an electron is Single Electron Transistor Technology. This fascinating technology showed enormous potential in the new physical effects of charge transport. Beside its innumerable benefits like - (a) simplicity of the device structures, (b) high integration density owing to its nano dimension, (c) high processing speed equal to electron speed, (d) low power consuming and (e) exquisite sensitivity which is about five orders of magnitude (is far better than conventional solid-state MOSFET transistors); SETs also have several open challenges waiting for elegant solutions. Thus SET is rising up to be indispensible in every sector of future electronic industry especially in digital electronics [1-12].

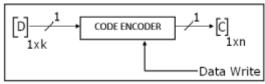

In Digital Communication System, a 'Linear code' is considered as one of the most efficient encoding and decoding algorithm. This technique is one of the easiest & simple techniques to detect and correct errors regarding its efficient algorithm. Extra parity bits used in this technique do not convey any information by themselves but using these extra parity bits it is possible to detect and correct errors in the received message. Thereby detecting and correcting the errors in the received message is sufficiently time consuming and much efficient. Moreover, Linear Block Codes has been extensively used in Digital Communication System where security and data integrity is of primary concern. Basically, the parity bits of linear block codes are linear combination of the message. Therefore, one can represent the encoder by a linear system described by matrices as shown in Fig.1 in the last section of this chapter.

Here, the aim is to realize SET based Linear Block coding technique and observe its performance to make it suitable for low power consuming next generation Digital Communication System.

http://www.ijesrt.com

#### Linear block code error correction technique Mathematical explanation

Using Parity Check code one can understand that error has occurred during the data transmission. But to know at which position the error has occurred Linear Block Coding technique is observed as better choice for serial data communication [13-17].

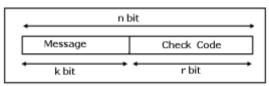

To transfer a 'k'-bit message further 'r'-bit is added making the total length of the message 'n'bit (Fig.2), where k < n. The message block is denoted as  $D = [d_1 \ d_2 \ \dots \ d_n]$  and the code word is likely to be  $C = [c_1 c_2 \dots c_n]$ . Thus the total number of message is 2<sup>k</sup>. Therefore, the possible code length for 2<sup>k</sup> message is 2<sup>n</sup>. Thus the valid message code length is  $(2^n - 2^k)$ . In the Transmitter side (also called encoder section) to generate the code word we have C = DG; where G = Generator Matrix denoted by  $[I_k: P]_{k \times n}$ . The  $I_k$  is the Identity matrix of order 'k' and P denotes an arbitrary matrix of order  $[k \times (n-k)]$ and  $C = [D]_{1 \times k} \times [G]_{k \times n}$ . For example if the message bit length is k=4 and the total length of the coded message is n = 7, then the valid message code length is  $(2^7 - 2^4)$ . For any 4-bit message the code word can be derived from the Table- 1. Considering the Table-3.1 the code for message  $D_{13}$  is derived from  $D_{13} = [1]$  $1 \ 0 \ 1] \rightarrow C_{13} = D \times G = [1 \ 1 \ 0 \ 1]$ 1 1 1]. The same code vector 'C' can also be achieved in the following way.

The Generator Matrix

Here the message [1 1 0 1] is multiplied with the Generator matrix and further it is XOR-ed. For detection and correction we use

$$R = C \bigoplus E$$

.....[3]

where E= Error Vector due to noise and R is message with error. Now let us consider that a noise has occurred within the communication channel that has changed the 3<sup>rd</sup> MSB. In other words, we can say that for the message [1 1 0 1], the Error Vector is calculated by XOR-ing the message with [0 0 1 0]; i.e., R= [1 1 0 1 1 1 1]  $\bigoplus$  [0 0 1 0 0 0 0] = [1 1 1 1 1 1 1]; thus at the receiving end we get the error

http://www.ijesrt.com

message which is the left most four bit, i.e., [1 1 1 1] instead of [1 1 0 1]. To detect the single bit error we perform the following calculations:-

$S = RH^{T}$  is the Error Syndrome. .......[4], where, H =  $[P_{(n-k)\times k}^{T} : I_{(n-k)}]_{(n-k)\times n}$  ......[5] and  $H^{T}$  is the transposition of H Matrix. If S is [0 0 0] then the message has no errors, else if S has any non-zero value in the matrix then the message contains error. The position of the error bit can be found through the usual way as stated below.

$$R = C \bigoplus E = \begin{bmatrix} 1 & 1 & 0 & 1, & 1 & 1 & 1 \end{bmatrix} \bigoplus \begin{bmatrix} 0 & 0 & 1 & 0, & 0 & 0 & 0 \end{bmatrix}$$

=  $\begin{bmatrix} 1 & 1 & 1 & 1, & 1 & 1 & 1 \end{bmatrix}, \dots, \dots, \begin{bmatrix} 6 \end{bmatrix}$

$$H = \begin{bmatrix} P^{T} : I_{3} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 1 & 0 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 & 0 & 1 \\ 1 & 1 & 1 & 1 & 0 & 0 & 1 \end{bmatrix}, \dots, \dots, \begin{bmatrix} 7 \end{bmatrix}$$

$$H^{T} = \begin{bmatrix} 1 & 0 & 1 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 0 & 0 \\ 0 & 0 & 1 \end{bmatrix}, \dots, \dots, \begin{bmatrix} 8 \end{bmatrix}, \text{Now}$$

$$S = RH^{T}$$

$$= \begin{bmatrix} 1 & 1 & 1 & 1, & 1 & 1 & 1 \end{bmatrix} \times \begin{bmatrix} 1 & 0 & 1 \\ 0 & 1 & 1 \\ 1 & 1 & 1 \\ 0 & 0 & 1 \\ 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix} = \begin{bmatrix} 1 & 1 & 1 \\ 1 & 1 & 1 \\ 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix}$$

The above calculations revealed that the error has occurred in the 3<sup>rd</sup> bit i.e., the 3<sup>rd</sup> MSB as presumed earlier. Thus one can easily detect the single error and correct the code using Linear Block Coding Technique. The same can be obtained for any size of messages.

#### Hardware realization using SET

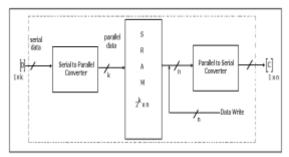

At the transmitting end the block that is generating the particular code word for a given input message is code encoder shown in Fig.3. It consists of one Serial to Parallel Converter, one SRAM and one Parallel to Serial converter. Implementation of these circuits using SET has been shown consequently.

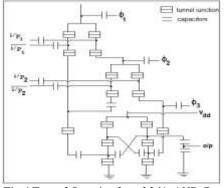

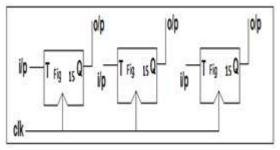

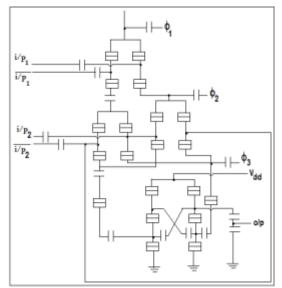

The Serial to Parallel converter is based on D Flip-Flops made from combination of AND gate and NOR gate. The Tunnel Junction based 2 input AND Gate, OR Gate and NOT Gate is designed in Fig.4, 5 and 6 respectively. Similarly the Tunnel

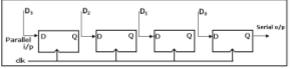

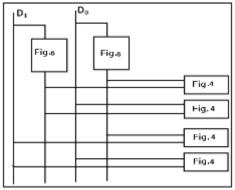

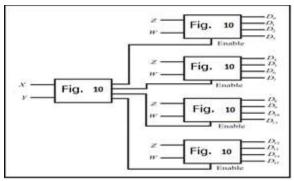

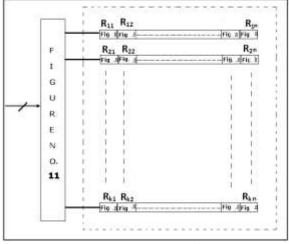

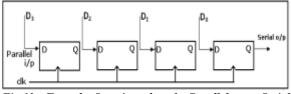

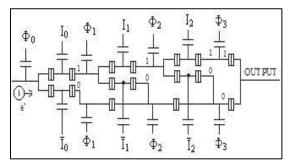

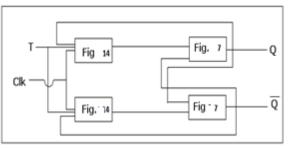

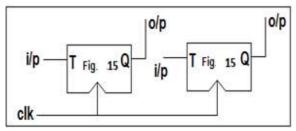

Junction based NOR Gate and the D Flip-Flop are shown in Fig. 7 and Fig. 8 respectively. Comprising all, the Serial to Parallel converter is designed (Fig. 9). The '2 to 4' decoder (Fig. 10) is used to design a '4 to 16' decoder (Fig. 11). Using Fig. 11 and Fig.8 the SRAM is designed (Fig 12). The Parallel to Serial converter is used using same D Flip Flop (Fig. 13). A 3 input AND gate is shown in Fig 14. Whereas Fig 16, 17 and 18 shows tunnel junction based 2-bit counter, tunnel junction based 3-bit counter and tunnel junction based XOR Gate respectively. This is how the Transmitter is generating the particular code word. This code word is containing the actual message.

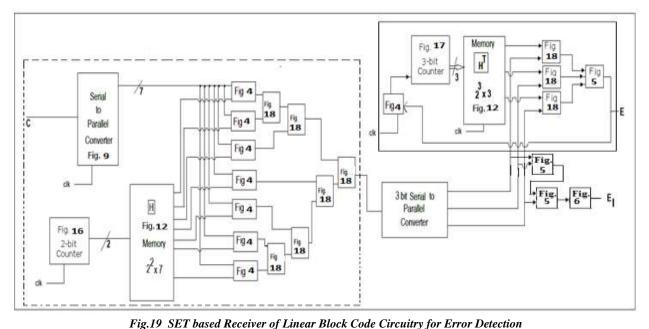

Similarly at the receiving end the circuitry that detects the error is shown in Fig 19, comprising of a Serial to Parallel Converter along with 7 AND Gates, T Flip-Flops, 2-bit Counter, 3-bit Counter, SRAM, XOR Gates designed using SET. The purpose of this circuitry is to detect error if any in the message and to correct it correspondingly and at the same time to make it low power consuming device. Most published research journals of Sarkar et.al demonstrate this novel approach in designing low power consuming nano electronic circuits for next generation operations [18-20].

#### The modus operandi of the proposed model

As stated earlier the code word is composed of the actual message and parity. Here we have shown example architecture with a 4-bit message; for this 4-bit total 16 messages (0000 to 1111) are available and correspondingly 16 code words are generated. The Table-1 at the last section shows code word for every message. In the code encoder circuitry the code word will be stored in the SRAM. As the number of code word is 16 so we need to take a  $2^4$  x 7 size of memory chip. The output of Serial to Parallel Converter is connected to the Address Bus of the SRAM. The messages are coming serially to the serial to parallel converter which is being fetched as parallel data by this converter and this data will be the address (message) of the SRAM, the stored data at each address i.e., the generated code will be sent to the Parallel to Serial Converter to make it serial data. Fig.3 shows a general architecture of this Code Encoder. The Data Write bus will be used to write the new code word to the SRAM when alterations are made in this circuitry.

Through the single channel the message within code word is coming serially to the error detection circuitry (Fig.19) where H SRAM (residing in the dashed block) will store the corresponding H matrix given in eq. [7]. Thereafter, eq.[8] will be

## ISSN: 2277-9655 Scientific Journal Impact Factor: 3.449 (ISRA), Impact Factor: 1.852

calculated through the dotted block of the same said Fig.19. After 3 cycle of the 2-bit counter the output of the dotted block will be stored in the 3-bit serial to parallel converter i.e., the Error Syndrome (S). Now, eq. [8] will be loaded in  $H^T$  SRAM placed in solid block of Fig.19. If 3-bit Serial to Parallel Converter data is [0 0 0] then E<sub>1</sub> is 1 which signifies message is unaffected by noise. When noise arises within the input code word the serial to parallel converter data (S) will check with the  $H^T$  data which is stored in  $H^T$  SRAM as stated above and if a match is found, the 3-bit counter will stop corresponding to E=0. Now the matched position of the SRAM will signify the error position as shown in eq.[9] above.

#### Comparatavie analysis of the proposed model

The modelling of SET based Linear Block Coding Error Correction technique was largely tested on Monte Carlo based simulation settings for its maximum exploitation. The proposed modelling of this SET based system which has been configured as an IC considerably reduces power consumption and is efficient enough to detect the unwanted errors at a quicker speed. As a result, a very high-speed but accurate computation is indeed attained with this newly proposed SET IC design. The power dissipation for switching a single bit is reduced considerably as shown in the Table-2 below is of few µW which is absolutely low when compared to conventional CMOS devices. Accordingly, it shows tremendous prospect of providing much more component density thereby reducing the future IC sizes. Thus among all other merits of SET based ICs the model reflects its robustness than any conventional CMOS based circuit.

| SI. | Techn | Propag | Faster | Power   | Consu      |  |  |  |  |  |

|-----|-------|--------|--------|---------|------------|--|--|--|--|--|

| No  | ology | ation  | times  | dissipa | me         |  |  |  |  |  |

|     | 0,    | Delay  |        | tion /  | Power      |  |  |  |  |  |

|     |       | time / |        | Gate    |            |  |  |  |  |  |

|     |       | Gate   |        |         |            |  |  |  |  |  |

| 1   | CMOS  | 12 ns  | 1      | 0.01 /  | 1          |  |  |  |  |  |

|     |       |        |        | 10-12   |            |  |  |  |  |  |

|     |       |        |        | mW      |            |  |  |  |  |  |

| 2   | SET   | 6 ns   | 2      | ~1µW    | $1/10^{3}$ |  |  |  |  |  |

Table 2. Comparison table for CMOS and SET

#### Conclusion

This SET device based Linear Block Code model efficiently detects error and consumes considerably less power compared to other existing error detection hardware models. Moreover, owing to its less complicated architecture the cost of the device can be quite low. Other concerned factors like time-

http://www.ijesrt.com

delay, integration density, speed and robustness of the model is of far better standard when matched to present day CMOS-TTL logic circuits. With the steady increase in SET fabrication technology such type of model will be designed efficiently by the nano device engineers in near future. Thus this model can be considered as a successful competent in next generation Digital Communication System.

#### **Reference:**

- [1] K. K. Likharev : IBM J. Res. Devel., vol 32, 144, 1988

- [2] P. Hadley, G. Lientschnig, and M. Lai, "Single-Electron Transistors," pp. 1–8

- [3] Ono, Y.; Takahashi, Y., "Single-electron passtransistor logic and its application to a binary adder" Symposium on VLSI Circuits, 2001. Digest of Technical Papers. 2001.

- [4] Degawa, K. et.al, "A single-electron-transistor logic gate family and its application - Part I: basic components for binary, multiple-valued and mixed-mode logic", 34th International Symposium on Multiple-Valued Logic, 2004.

- [5] Lageweg, C. ; Cotofana, S. ; Vassiliadis, S., "Binary addition based on single electron tunneling devices" 4th IEEE Conference on Nanotechnology, 2004.

- [6] Sulieman, M.H.; Beiu, V. "On single-electron technology full adders", IEEE Transactions on Nanotechnology, Volume:4, Issue: 6, 2005.

- [7] S.J. KIM et al., "SINGLE-ELECTRON LOGIC CELLS AND SET/FET HYBRID INTEGRATED CIRCUITS", JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL.6, NO.1, MARCH, 2006

- [8] Lee, C.K.; Kim, S.J.; Shin, S.J.; Choi, J.B.; Takahashi, Y., "Single-electron-based flexible multivalued logic gates", Applied Physics Letters, Volume:92, Issue: 9, 2008.

- [9] Bing-cai Sui et.al., "Reconfigurable singleelectron transistor logic gates", 9t<sup>h</sup> International Conference on Solid-State and Integrated-Circuit Technology, 2008.

- [10] Gerousis, C. ; Grepiotis, A., "Programmable logic arrays in single-electron transistor technology" International Conference on Signals and Electronic Systems, 2008.

- [11] Jo-Won Lee ; Moonkyung Kim, "Roadblocks to Tera-level nanoelectronics", 9<sup>th</sup> International Conference on Solid-State and Integrated-Circuit Technology, 2008.

- [12] Nakajima, F. et.al., "Single-electron AND/NAND logic circuits based on a selforganized dot network", Applied Physics Letters,

Volume:83, Issue: 13, 2008.

- [13] Chaudhari, P.; Khandani, A.K., "Using the Fourier transform to compute the weight distribution of a binary linear block code", IEEE Communications Letters, Volume: 5, Issue: 1, 2001

- [14] Sankaranarayanan, S.; Vasic, B. "Iterative Decoding of Linear Block Codes: A Parity-Check Orthogonalization Approach", IEEE Transactions on Information Theory, Volume:51, Issue: 9, 2005.

- [15] Hadi, A.S., "Linear block code decoder using neural network", IEEE International Joint Conference on Neural Networks, 2008. IJCNN 2008. (IEEE World Congress on Computational Intelligence).

- [16] Kai Yang ; Xiaodong Wang ; Feldman, J., "A New Linear Programming Approach to Decoding Linear Block Codes", IEEE Transactions on Information Theory, Volume:54, Issue: 3, 2008

- [17] Bhattar, R.K.; Ramakrishnan, K.R.; Dasgupta, K.S., "On computation of minimum distance of linear block codes above 1/2 rate coding" IEEE International Conference on Wireless Communications, Networking and Information Security (WCNIS), 2010.

- [18] Subir Kumar Sarkar et.al, "Design and Simulation of 2-to-4 Decoder Using Single Electron Tunnelling Technology based Threshold Logic Gate" Journal of Electron Devices, Vol. 9, 2011, pp. 342-351.

- [19] Subir Kumar Sarkar et.al, "Bi-directional Sequence Generator Using Single Electron Device Based Threshold Logic Gates", Journal of Nanoelectronics and Optoelectronics, Volume 5, Number 3, December 2010, pp. 323-331.

- [20] Subir Kumar Sarkar et.al.," SET-MOS Hybrid Logic Circuit", International Journal of Recent Trends in Engineering& Technology, Vol.4, pp-42-45,2010.

Author Biblography

Jayanta Gope

Prof. Jayanta Gope, B.E., PhD (Nanotechnology) from Jadavpur Univ. India, is presently at CSET. His field of interest includes Nano device modeling, SET/ SED, Spintronic Devices, Hybrid CMOS-SET. He has several international publications in these field.

http://www.ijesrt.com

## ISSN: 2277-9655 Scientific Journal Impact Factor: 3.449 (ISRA), Impact Factor: 1.852

List of Figures

Fig.1 Linear Block Coding Technique Diagram

Fig.2. Message bit length

Fig.3 Code Encoder

Fig.4 Tunnel Junction based 2 i/p AND Gate

Fig.5 Tunnel Junction based 2 i/p OR Gate

http://www.ijesrt.com

Fig.6 Tunnel Junction based 2 i/p NOT Gate

Fig.7 Tunnel Junction based 2 i/p NOR Gate

Fig.8 Tunnel Junction based DFlip Flop

Fig.9 Tunnel Junction based 4 bit Parallel to Serial Converter

Fig.10 Tunnel Junction based 2<sup>2</sup> X 4 Decoder

Fig.11 Tunnel Junction based 4 to 16 Decoder using 2 to 4 Decoder

Fig.12 Tunnel Junction based SRAM  $2^k X n$

Fig.13 Tunnel Junction based Parallel to Serial Converter

Fig.13 Tunnel Junction based 3 input AND Gate

Fig.15 Tunnel Junction based T Flip-Flop

Fig.16 Tunnel Junction based 2-bit Counter

Fig. 17 Tunnel Junction based 3-bit Counter

Fig. 18 Tunnel Junction based XOR Gate

http://www.ijesrt.com

| Table- 1. Code word for any 4-bit message |                |                       |                       |    |             |                       |                |            |            |                       |                       |                       |                |

|-------------------------------------------|----------------|-----------------------|-----------------------|----|-------------|-----------------------|----------------|------------|------------|-----------------------|-----------------------|-----------------------|----------------|

| <sup>[D]</sup> →                          | $\mathbf{d}_1$ | <b>d</b> <sub>2</sub> | <b>d</b> <sub>3</sub> | d4 |             | [C]                   | С <sub>6</sub> | <b>C</b> 5 | <b>C</b> 4 | <b>c</b> <sub>3</sub> | <b>c</b> <sub>2</sub> | <b>c</b> <sub>1</sub> | C <sub>0</sub> |

| D <sub>0</sub>                            | 0              | 0                     | 0                     | 0  |             | C <sub>0</sub>        | 0              | 0          | 0          | 0                     | 0                     | 0                     | 0              |

| <b>D</b> <sub>1</sub>                     | 0              | 0                     | 0                     | 1  |             | C <sub>1</sub>        | 0              | 0          | 0          | 1                     | 0                     | 0                     | 1              |

| <b>D</b> <sub>2</sub>                     | 0              | 0                     | 1                     | 0  |             | <b>C</b> <sub>2</sub> | 0              | 0          | 1          | 0                     | 1                     | 1                     | 1              |

| <b>D</b> <sub>3</sub>                     | 0              | 0                     | 1                     | 1  |             | <b>C</b> <sub>3</sub> | 0              | 0          | 1          | 1                     | 1                     | 1                     | 0              |

| D <sub>4</sub>                            | 0              | 1                     | 0                     | 0  |             | <b>C</b> <sub>4</sub> | 0              | 1          | 0          | 0                     | 0                     | 1                     | 1              |

| <b>D</b> <sub>5</sub>                     | 0              | 1                     | 0                     | 1  |             | C <sub>5</sub>        | 0              | 1          | 0          | 1                     | 0                     | 1                     | 0              |

| D <sub>6</sub>                            | 0              | 1                     | 1                     | 0  |             | <b>C</b> <sub>6</sub> | 0              | 1          | 1          | 0                     | 1                     | 0                     | 0              |

| <b>D</b> <sub>7</sub>                     | 0              | 1                     | 1                     | 1  |             | <b>C</b> <sub>7</sub> | 0              | 1          | 1          | 1                     | 1                     | 0                     | 1              |

| <b>D</b> <sub>8</sub>                     | 1              | 0                     | 0                     | 0  |             | C <sub>8</sub>        | 1              | 0          | 0          | 0                     | 1                     | 0                     | 1              |

| D9                                        | 1              | 0                     | 0                     | 1  |             | C9                    | 1              | 0          | 0          | 1                     | 1                     | 0                     | 0              |

| <b>D</b> <sub>10</sub>                    | 1              | 0                     | 1                     | 0  |             | C <sub>10</sub>       | 1              | 0          | 1          | 0                     | 0                     | 1                     | 0              |

| <b>D</b> <sub>11</sub>                    | 1              | 0                     | 1                     | 1  |             | C <sub>11</sub>       | 1              | 0          | 1          | 1                     | 0                     | 1                     | 1              |

| <b>D</b> <sub>12</sub>                    | 1              | 1                     | 0                     | 0  |             | C <sub>12</sub>       | 1              | 1          | 0          | 0                     | 1                     | 1                     | 0              |

| <b>D</b> <sub>13</sub>                    | 1              | 1                     | 0                     | 1  |             | C <sub>13</sub>       | 1              | 1          | 0          | 1                     | 1                     | 1                     | 1              |

| <b>D</b> <sub>14</sub>                    | 1              | 1                     | 1                     | 0  |             | C <sub>14</sub>       | 1              | 1          | 1          | 0                     | 0                     | 0                     | 1              |

| <b>D</b> <sub>15</sub>                    | 1              | 1                     | 1                     | 1  | $ \square $ | C <sub>15</sub>       | 1              | 1          | 1          | 1                     | 0                     | 0                     | 1              |

| <b>,</b> | <br> | <br>•J |     | <br> | <i>j</i> , | <br> |

|----------|------|--------|-----|------|-----------------------------------------------------------------------------------------|------|

|          |      |        | ~ . |      |                                                                                         |      |

http://www.ijesrt.com